Date: Jan 13, 2026 Read: 428

Share:

The rapid advancement of AI is emerging as a key driver of global storage market growth, fueling surging demand across the entire memory and storage stack—from DRAM and NAND to SSDs/HDDs.

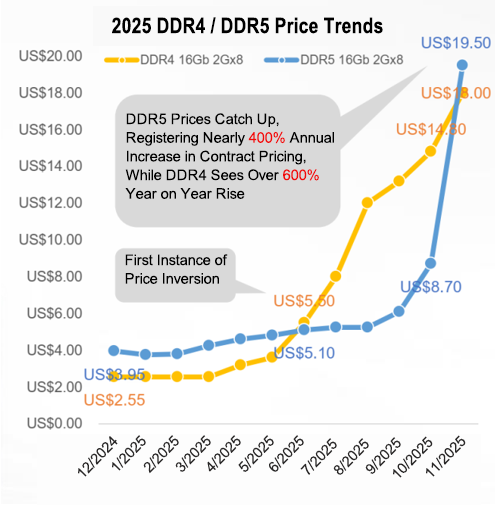

Currently, the production shift from DDR4 to DDR5 is leading to increasingly tight DDR4 supply. This uncertainty is already impacting the server and data center industries, posing challenges to their sustained development.

• Rising Costs: Shortages and price hikes for DDR4 are directly driving up procurement and operational costs for enterprise IT infrastructure.

Source: TrendForce

• Performance Bottlenecks: Next generation CPU platforms demand higher memory bandwidth. Continuing to rely on DDR4 will fail to fully unleash the new platforms' computing potential, creating a performance bottleneck. On the other hand, many legacy platforms still in service lack hardware level support for DDR5 (e.g., CPU memory controllers or motherboard slots), fundamentally hindering a smooth transition to DDR5.

• Supply Chain Risk: Relying on DDR4 components nearing end of life exposes enterprises to long term risks in product planning and supply chain stability.

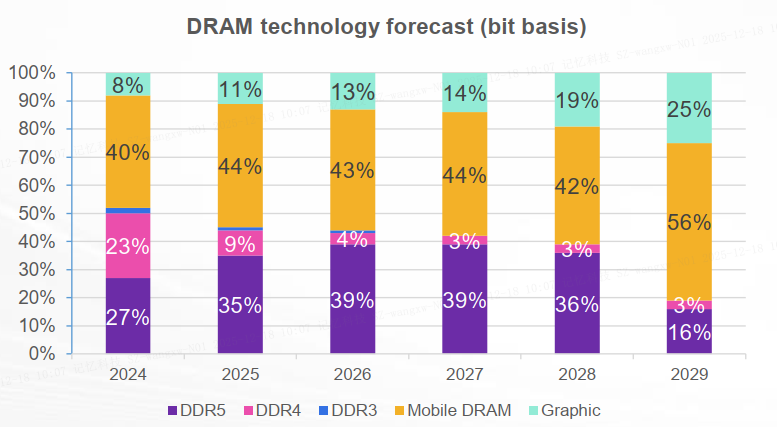

*Trend Forecast: The Application Share of DDR4 is Expected to Decline Significantly

Source: TrendForce, Omdia

This cascade of effects demonstrates that merely waiting or maintaining the status quo is no longer viable. The industry urgently needs a smooth and efficient upgrade path that bridges the present and the future while addressing both performance demands and cost considerations.

I. Union Memory's Full PCIe 5.0 eSSD Portfolio Supports DDR5, Driving Industry Breakthrough

Based on a deep understanding of the upgrade bottlenecks described above, Union Memory has made forward-looking strides in new-generation enterprise SSDs: being the first to adopt advanced SOC controllers with native DDR5 support. This critical design shift integrates DDR5 compatibility and signal integrity assurance at the chip design stage —rather than through later adaptation—ensuring optimal support for DDR5 memory from the ground up. This approach delivers:

Higher Performance without Compromise: It fully unleashes DDR5’s bandwidth potential, providing the SSD with extreme data caching throughput.

Stable Supply with Lower Risk: Designs based on such SOCs enable Union Memory’s eSSDs to seamlessly adapt to the latest CPU platforms supporting DDR5, helping customers bypass DDR4 supply chain constraints and directly build future ready computing infrastructure.

Adopting an advanced SOC controller is only the first step in embracing DDR5. Recognizing that DDR5, as a new technology, presents critical challenges in signal integrity and system compatibility - challenges that must be resolved for enterprise-grade adoption, Union Memory adheres to an enterprise stability first principle. In dedicated compatibility labs, the company has conducted rigorous DDR5 specific signal testing on the new-generation UH8 series SSD products, ensuring absolute stability in real world, complex operating environments.

II. Defining the Absolute Standard of Enterprise Stability Through Rigorous Validation

The transition from DDR4 to DDR5 represents a systematic challenge that must be supported by stringent testing and data to prove its maturity.

While DDR5's dual channel design improves data read/write efficiency and overall system performance, it also imposes more demanding requirements on address signal speed and timing compared to DDR4. As a result, address signal testing is one of the core steps in ensuring system stability and data integrity.

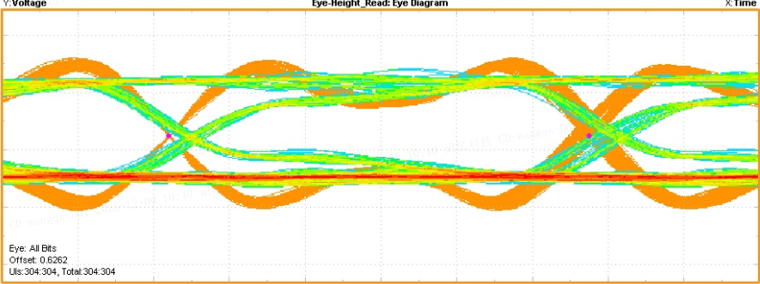

Union Memory has conducted full-range operational testing on address signals, covering signal integrity, timing, and multi platform scenarios. As demonstrated by the address signal eye diagram below, the DDR5 address signals of Union Memory’s UH8 series SSDs fully comply with the JESD79 5 protocol specification.

Eye Diagram of DDR5 Address Signals for the New‑Generation UH8 Series

Compared to DDR4, the higher data rate of DDR5 significantly amplifies signal losses, reflections, and crosstalk along transmission paths. Even minor signal distortion can lead to data errors, resulting in system performance degradation or silent data corruption. In DDR5, eye diagram testing for data signals in both read and write directions is therefore essential to ensure data transmission integrity and product reliability.

Union Memory has established a comprehensive, closed‑loop validation framework covering both read and write paths to ensure highly stable bidirectional data transmission.

• Write‑direction data signal eye diagram testing verifies that the UH8 series SSDs can accurately deliver write commands.

Eye Diagram of DDR5 Write‑Direction Data Signals for the New‑Generation UH8 Series

• Read‑direction data signal eye diagram testing verifies that the UH8 series SSDs can accurately return read data and correctly receive and parse it without errors.

Eye Diagram of DDR5 Read‑Direction Data Signals for the New‑Generation UH8 Series

III. Enterprise Grade and Consumer Grade Dual Engine Drive, Providing Core Support for Full Domain Application Scenarios

Union Memory UH812a/UH832a: Extreme Performance, Leading High Speed Computing

The UH812a/UH832a, a PCIe Gen5 SSD, is designed for mission critical workloads such as AI training, real time databases, and high performance computing. It delivers sequential read/write bandwidth of up to 14.9 GB/s, combined with multi layer reliability and intelligent management features, ensuring stable low latency operation even under high pressure environments—unlocking the full potential of computing platforms.

Across various AI scenarios, the UH812a/UH832a series delivers outstanding performance support, meeting the stringent requirements of AI related industry applications for storage systems.

Furthermore, in a previous authoritative review by an independent third party professional organization, Union Memory UH812a was confirmed to operate smoothly in a DDR5 environment, providing solid assurance for enterprise upgrade and deployment.

Union Memory AE531: Redefining the Consumer QLC Storage Experience

The architecture of Union Memory's consumer SSDs is streamlined for efficiency: designed without DRAM dependency, it maintains strong performance while significantly optimizing overall cost. Building on this foundation, Union Memory introduces the highly competitive consumer grade AE531, offering an even more compelling choice for client storage solutions.

As Union Memory's first consumer QLC SSD, the AE531 leverages a DRAM less design and the high density advantages of QLC NAND to deliver lower power consumption and enhanced endurance. The AE531 also excels in compatibility, fully supporting x86 and various non x86 architecture platforms to ensure stable, reliable operation across diverse hardware environments.

In terms of performance, the AE531 combines innovative firmware algorithms with deep integration of HMB (Host Memory Buffer) technology to effectively improve data read write efficiency. In QLC direct write mode, the 1TB model achieves sequential write speed of 160 MB/s, fully meeting the demands of diverse scenarios such as daily office tasks, digital entertainment, and light creative workloads.

Tackling the challenges of the DDR5 upgrade cycle, Union Memory is driving storage technology innovation through forward looking R&D investment and will soon launch a new 8 channel DSSD based on its in house developed SOC controller. By leveraging its comprehensive advantages in energy efficiency, density, and reliability, this solution will directly empower industry clients to achieve optimal Total Cost of Ownership (TCO).